《本研究のポイント》

【研究概要】

名古屋大学未来材料・システム研究所の宇治原 徹 教授、理化学研究所革新知能統合研究センターの沓掛 健太朗 客員研究員(現 名古屋大学未来材料・システム研究所 准教授)、グローバルウェーハズ・ジャパン株式会社の永井 勇太 参事、アイクリスタル株式会社の髙石 将輝 代表取締役、関 翔太 取締役技術統括、ソニーセミコンダクタマニュファクチャリング株式会社の谷川 公一主幹技師 らの研究グループは、仮想空間上に構築したデジタルツインを接続して高速に最適化するプラットフォーム(メタファクトリー)を用いて、Siウェーハ製造からCIS製造までの一貫したプロセス全体最適化を行いました。

先端半導体デバイス開発では、短期間での性能向上が求められますが、従来型の個々の工程の最適化では限界があります。特に近年、Siウェーハ内部の不純物濃度分布や欠陥密度分布をデバイス構造に合わせて適切に作り込む必要が判明し、プロセス全体での最適化が重要となっています。しかし、企業の壁を越えて、ウェーハ製造とデバイス製造とが一体となって機密性の高い情報を共有した上で、膨大なプロセスパラメータの最適化を短時間で行うことは困難でした。

本研究では、Siウェーハ製造プロセスからCIS製造プロセスまでのデジタルツインを仮想空間上に構築して最適化することで、企業の壁を越えた最適化を実現しました。さらに従来のシミュレーションを用いた最適化と比較して、要する時間を約1/1000に短縮しました。本成果は、企業横断での最適化の必要性を実証するものであり、またCISのみならずさまざまな半導体材料・デバイスに共通して展開可能な方法です。

本研究成果は、2025年3月17日に第72回応用物理学会春季学術講演会にて発表されました。

【研究の背景】

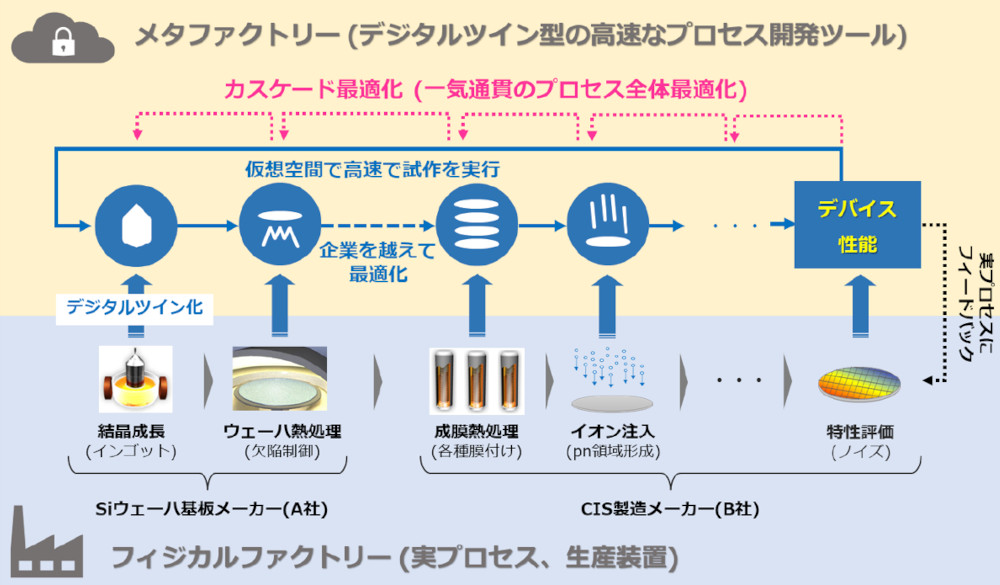

先端半導体デバイスの新製品開発では、短い開発サイクルの中での性能改善が求められますが、従来型の個々のデバイス製造工程内での最適化では改善できる性能に限界があります。加えて近年、デバイス性能を極限まで向上させるためには、Siウェーハ内部の不純物濃度分布や欠陥密度分布をデバイス構造に合わせて適切に作りこまなければならないことが明らかになってきました。これらの理由から、半導体デバイス製造工程においては、上流のSiウェーハ製造から下流のデバイス製造までを通じて最適化することがますます重要になっています(図1)。しかし現状では、企業の壁を越えて、ウェーハ製造とデバイス製造とが一体となってプロセス最適化を行う仕組みは存在しません。その理由は、企業間でプロセスデータやデバイス特性データといった極めて機密性の高い情報を共有した上で、膨大なプロセスパラメータの最適化が必要となるためです。

図1 半導体デバイス製造工程の模式図。結晶欠陥注3)分布の精密な作り込みのためには、Siウェーハ製造からデバイス製造まで通じたプロセス全体の最適化が必要。

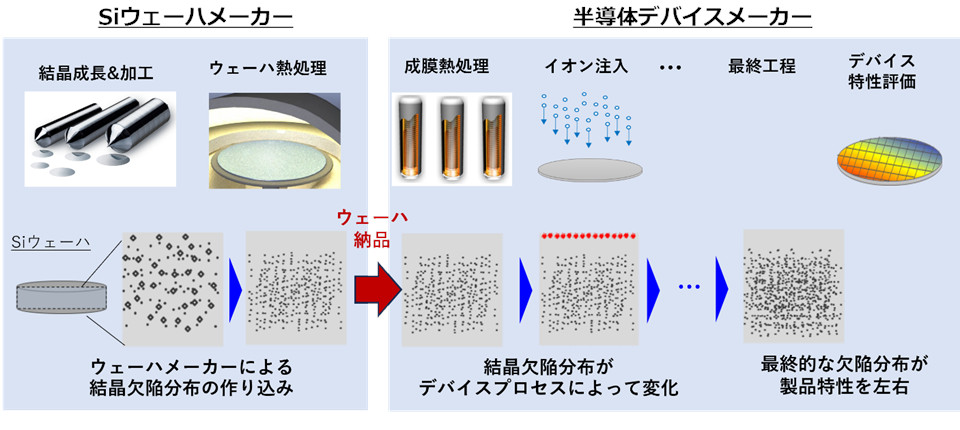

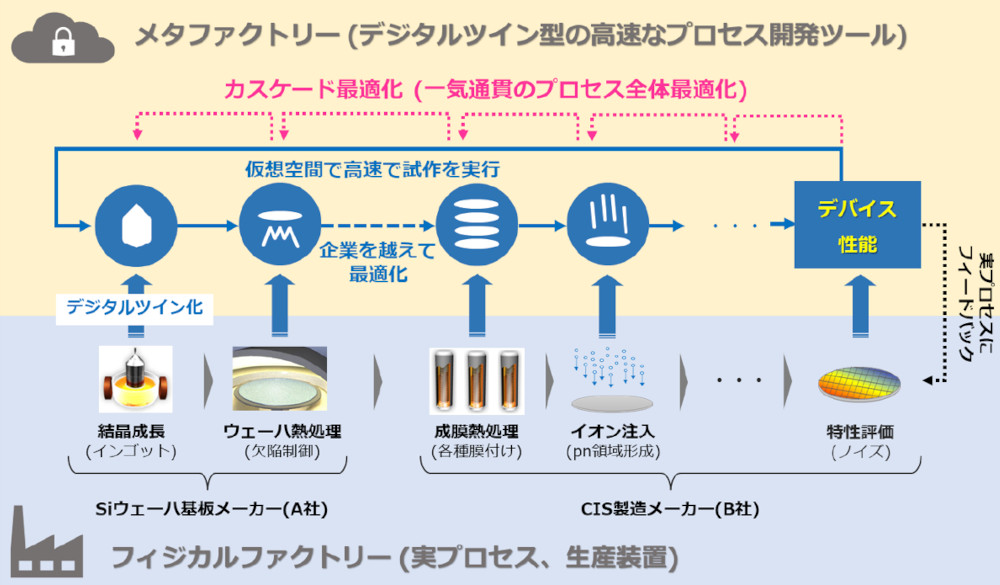

本研究では、材料からデバイスまで企業横断でプロセスを最適化することの有効性を検証するために、Siウェーハメーカーであるグローバルウェーハズ・ジャパン株式会社と半導体デバイスメーカーであるソニーセミコンダクタマニュファクチャリング株式会社が共同で、先端CMOSイメージセンサー(CIS)のノイズ特性改善をモデルケースとし、Siウェーハ製造プロセスからCIS製造プロセスまでの一貫したプロセス全体最適化を行いました。この最適化を行う計算技術を開発するために、アイクリスタル株式会社がデジタルツインを構築し、理化学研究所および名古屋大学が効率的な最適化アルゴリズムの開発を行いました。また、このようなプロセス全体最適化の技術をCISの課題解決のみにとどめず、さまざまな半導体材料から半導体デバイスへの拡張させるために、アイクリスタル株式会社がプロセス全体最適化のための新たなプラットフォーム(メタファクトリー)を構築しました。

図2 メタファクトリーの模式図。仮想空間上に構築したデジタルツインを接続して、企業を超えた全体最適化を行う。

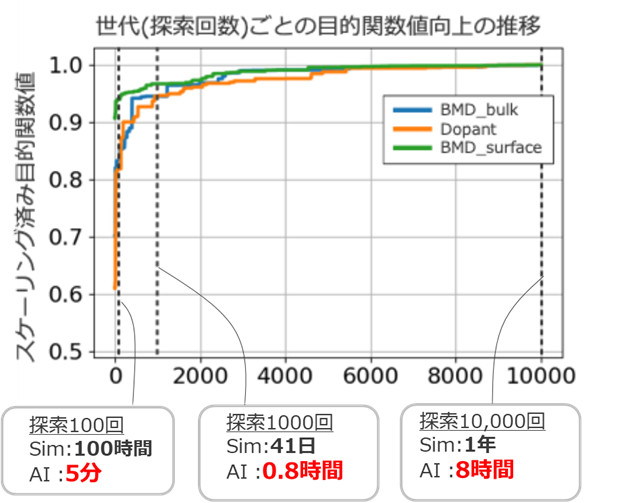

図3に最適化結果の一例を示します。BMD(Bulk Micro Defect)と呼ばれる欠陥の密度分布を理想的な分布に近づけるための目的関数(BMD_bulkおよびBMD_surface)、および、ドーパント濃度分布を理想的な分布に近づけるための目的関数(Dopant)に対して最適化を行った結果です。縦軸は値が1に近いほど理想分布に近いことを表します。横軸は最適化における試行回数(計算回数)です。この最適化では、最適条件を取得する(目的関数の向上が収束する)まで、1万回以上の条件探索が必要であることが分かります。この1万回の条件探索を従来のシミュレーション(Sim)を用いて行った場合は、1年を要します。製品開発のための最適化は、制約条件などを変更して何度も行う必要があるため、シミュレーションを用いた最適化では数年を要してしまい、最適化期間を製品開発サイクルに収めることができません。一方、今回開発したデジタルツイン(AI)を用いた最適化では、1万回の条件探索を8時間で完了することができます。このような高速なデジタルツインを用いることで、Siウェーハ製造からCIS製造までの最適なプロセス条件を短期間で取得することができました。

図3 最適化の結果。縦軸の目的関数の値が1に近いほど理想に近い。

【成果の意義】

本研究において得られた半導体プロセスの全体最適化の成果は、企業横断での最適化の必要性を実証するものです。本手法は、CISのみならずさまざまな半導体材料から半導体デバイスに共通して展開可能な方法です。また、機密性の高いプロセスデータやAIモデルの秘匿をいかに維持した状態で企業横断での全体最適化を実現するかが今後の課題です。

本研究は、NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)の委託業務で、令和5年度から令和6年度に「NEDO先導研究プログラム/新産業・革新技術創出に向けた先導研究プログラム/半導体プロセスメタファクトリーの基盤技術開発」として行われたものです。

【用語説明】

注1)CIS:

CMOSイメージセンサーを指し、カメラの撮像素子のこと。スマートフォン、デジタルカメラ、監視カメラ、産業用センサーなど、多様な用途で用いられている。(↑ 本文に戻る)

注2)デジタルツイン:

コンピュータ内に構築された実際の工程のモデル。(↑ 本文に戻る)

注3)結晶欠陥:

結晶格子の乱れ。原子空孔や格子間原子、不純物原子、転位、析出物など。結晶欠陥自身は半導体デバイス特性を低下させる要因となるが、デバイス活性領域外に適切に形成された結晶欠陥は活性領域の金属不純物を捕獲する(ゲッタリング)など、半導体デバイス特性の向上に寄与する(↑ 本文に戻る)

【学会情報】

第72回応用物理学会春季学術講演会

17a-K505-1

カスケード工程におけるSiウェーハ内部の酸素析出物分布のデータ同化

〇楠木 琢也1、阿部 諄汰1、永井 勇太1、須藤 治生1、岩城 浩也1、高須 理栄1、番場 博則1、泉妻 宏治1、前田 進2、関 翔太2

(1.グローバルウェーハズ・ジャパン、2.アイクリスタル)

17a-K505-2

半導体製造における企業間を跨いだデジタルツインによるウェーハ・デバイスプロセスの全体最適化

〇関 翔太1,4、中西 佑児1、松岡 毅1、前田 進1、髙石 将輝1、楠木 琢也2、永井 勇太2、永倉 大樹3、谷川 公一3、沓掛 健太朗4、宇治原 徹1,4

(1.アイクリスタル、2.グローバルウェーハズ・ジャパン、3.ソニーセミコンダクタマニュファクチャリング、4.名大)

17a-K505-3

半導体熱処理条件の最適化における既存条件を考慮した目的関数の検討

笠原 亮太郎1、〇沓掛 健太朗1,2、原田 俊太1、宇治原 徹1、関 翔太3、高石 将暉3、永井 勇太4

(1.名大、2.理研、3.アイクリスタル、4.グローバルウェーハズ・ジャパン)

研究者連絡先

東海国立大学機構 名古屋大学

未来材料・システム研究所

教授 宇治原 徹(宇治原研究室)

E-mail: ujihara[at]nagoya-u.jp

※メール送信の際は[at]を@に置き換えてください。

東海国立大学機構 名古屋大学

未来材料・システム研究所

准教授 沓掛 健太朗

E-mail: kutsukake.kentaro.c3[at]f.mail.nagoya-u.ac.jp

※メール送信の際は[at]を@に置き換えてください。